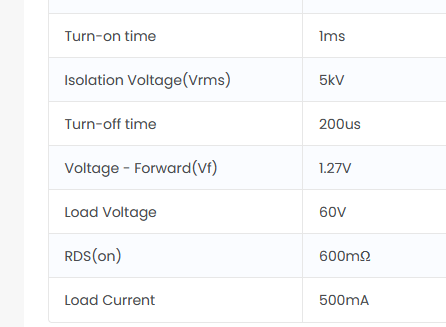

Ultra-low Rds(on) FETs like that have come a long way, but they’re one part where the reality of using them differs the most from the datasheet top-line specs.

That 135A is at a case temp of 25 degrees C which isn’t realistically achievable in any situation I’ve seen.

The high Tc value is normally what I’d start from, so 95A here. From there it may also not be practical to achieve that due to thermal issues. 2degC/W Tj-c.

So to use that thing effectively, you need to start sleuthing through the specifications.

In the tables it has a lot of the specs at 20A and 25degC. For a Vgs of 10V you’ve got 1.7mR typical, 2.1mR max at 20A. So we start with the 2.1mR number.

Then there’s figure 6 which shows you Rds(on) vs drain current at 25degC. You can check the numbers from the table above by looking at the 20A value. It looks like it’s around 1.7mR so that’s typical. At 100A it looks more like 1.8mR or 1.85mR but I’d normally break out the plot digitizer to figure that out. So we say it’s 1.85/1.7 = ~9% worse Rds(on) at 100A as at 20A. Apply that same scale to the worst case Rds(on) from above and we’re at 2.28mR.

We can then go to figure 7 and look at how it changes with temperature. It rises with temperature which means we know we need to be careful and design with some overhead because it’s quite possible to have it go into thermal runaway. FET gets hotter, losses get higher. Losses get higher, FET gets hotter, etc. This is a normalized graph so we double check that our starting point is 25C, which it is, then look at say 150C as a good ‘worst case’ scenario. Looks like a 1.75 factor so we can take 2.28mR * 1.55 = 3.98mR.

100A at 3.98mR is 39.8W. Given the Tj-c above that’s 70 degrees C junction to case, so to hit that 150 degree junction temp above we have to keep the case to 70 degrees C. With a 50 degree ambient that’s 20 degrees of thermal margin to go from the device case to ambient. That’s 0.5degC/W even before ignoring the fact that there’s no thermal specific pad on the device and you need to pull the heat out through the PCB. As an example, you can take a look at heat-sink specs and see what a 0.5degC/W heat-sink looks like, it’ll be pretty meaty, and that’s usually specified assuming an even heat load on the surface or a specific package mounted to it, which this will be very much neither.

By comparison, a TCM2209 is a similar package with a similar thermal pad and that’s only rated to dissipate maybe 3-4W?

It’s still pretty impressive, but I’d say it’s closer to a 20A output, ‘maybe’, and very much depending on heatsink capability.