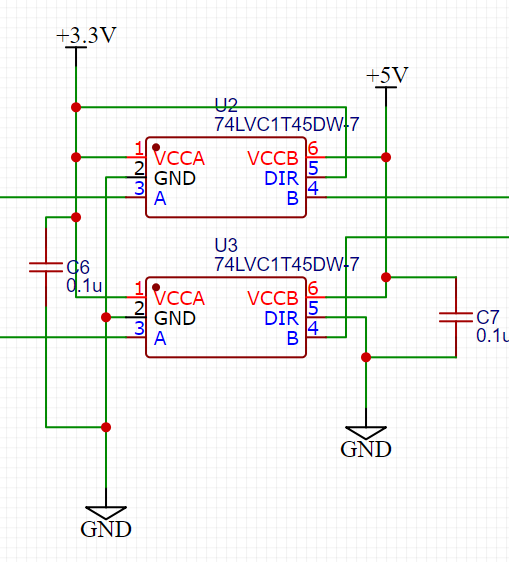

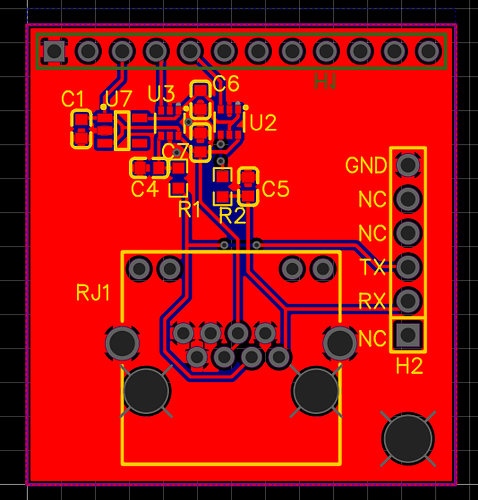

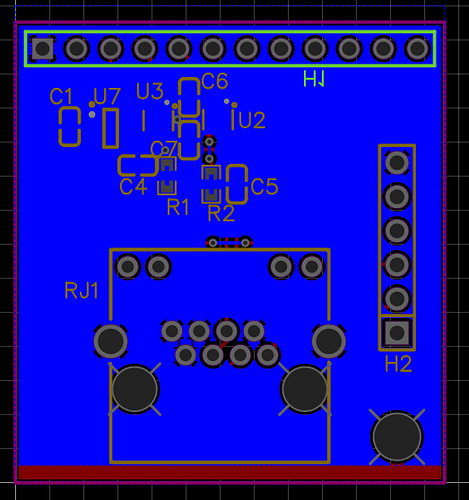

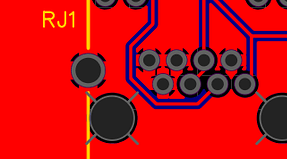

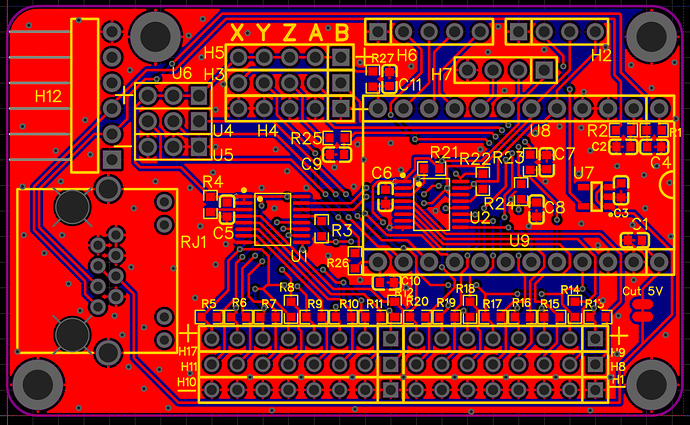

I would definitely use one decoupling cap per translator IC. The goal is to have one capacitor as physically close to the power/ground terminals as possible (ideally within a mm or 2, 5mm total ‘path’ length) so that the higher frequency components of a fast edge rate will be supplied from that capacitor, rather than from one further away down a higher inductance path that will cause the supply voltage to drop briefly (or the ground node to rise briefly) on transition. It’s a geometric consideration more than it is an electrical/schematic based consideration. If you end up with 2 decoupling caps that are basically right next to each other than you could remove one, but I wouldn’t bother. 100nF capacitors are probably the cheapest and most commonly made part on the board, so they’re likely less than a cent each.

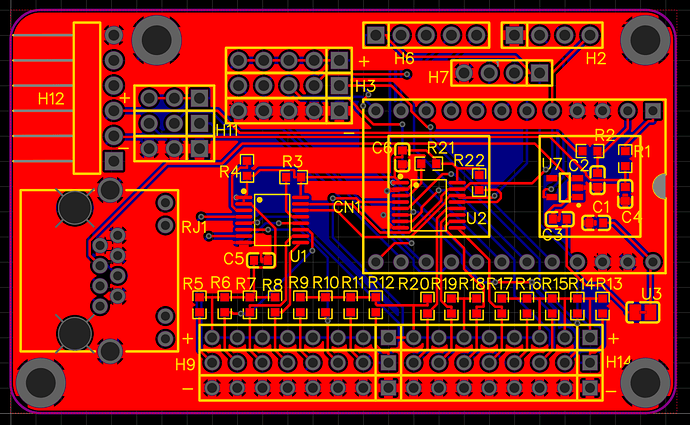

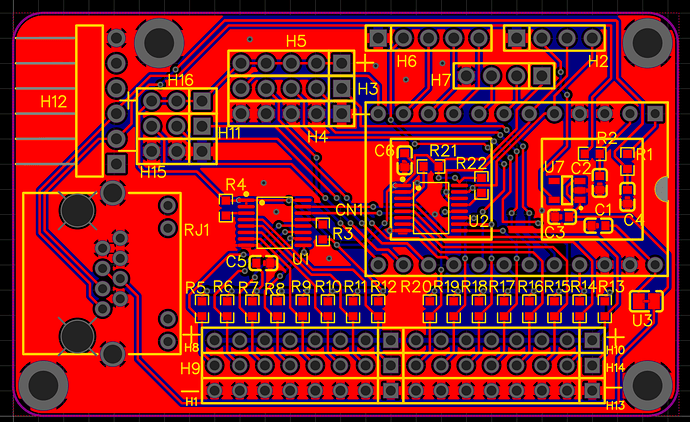

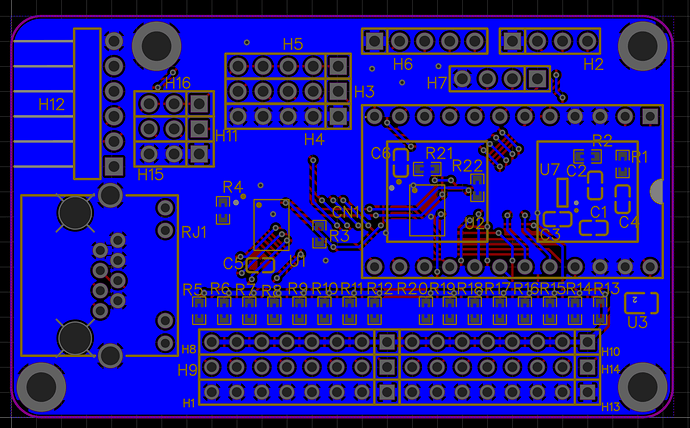

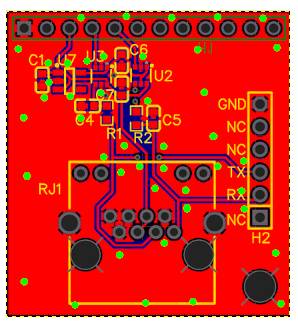

I would also use decoupling caps every place that there’s a VCC signal going out on a header, typically. Partly for decoupling, partly to filter any noise from coming back down the cables and into your supply lines, which isn’t that different of a purpose to decoupling, really. For the banks of headers like H1, H16, H5 then I’d just put a single one there.

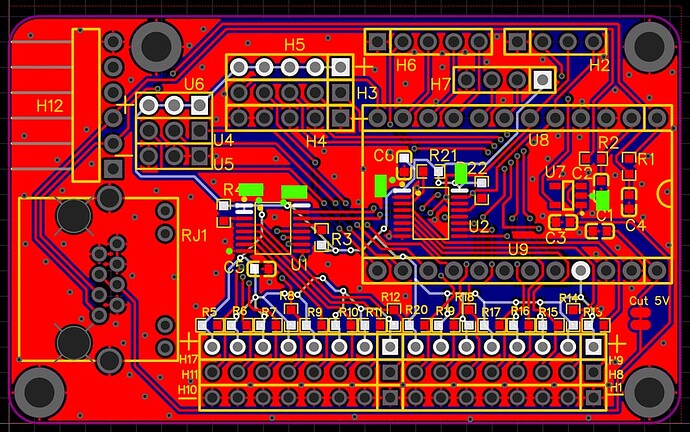

Just a weird thought with the layout of those headers, in future I’d probably do them as 8 instances of 1x3 headers to closer match the ‘intention’ of their use. That way you’re guaranteed that each header will be the correct dimensions because they’re a single part, you’ll have flexibility to move them around a little if needed and it will make the schematic much more readable, which is key to avoiding mistakes. I wouldn’t change it now. It’s baking my brain a little, though.

With header H6, where was that heading to? I’ve lost the plot a little bit with this design, sorry. I ask because it doesn’t currently have a ground net routed to it.

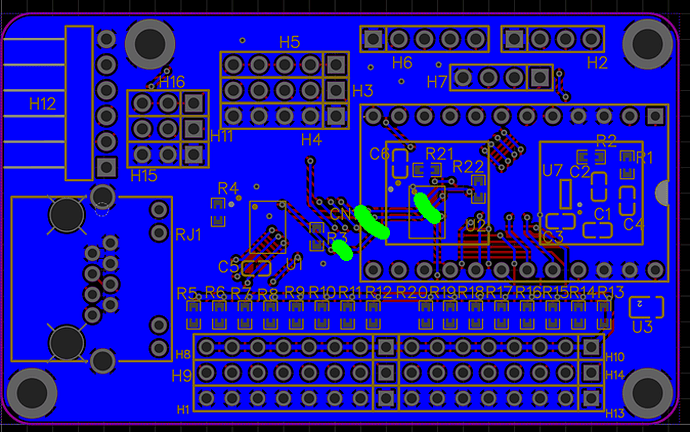

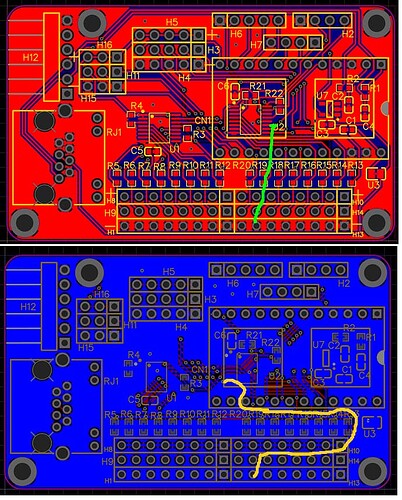

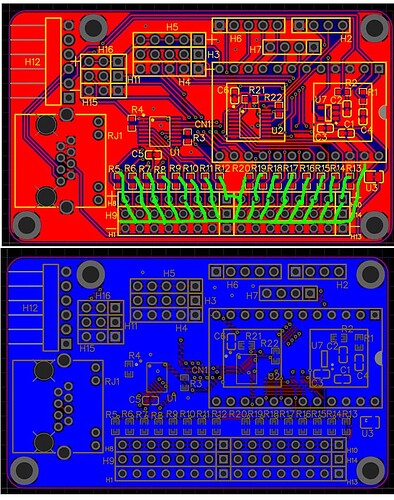

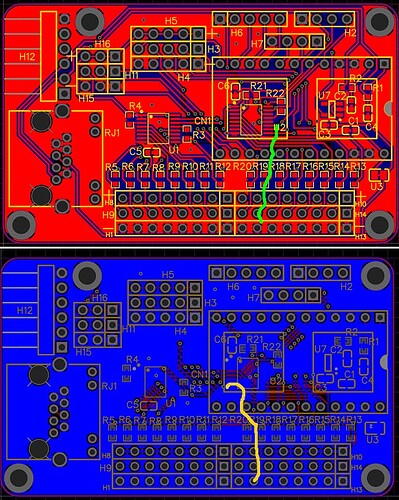

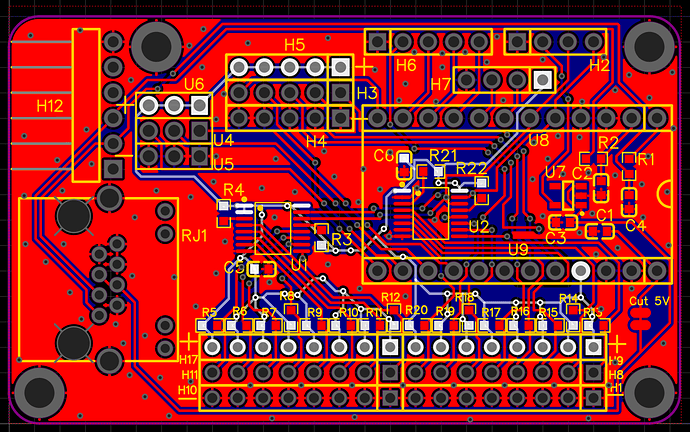

Was this just a test to see how it turned out? Auto-routers typically turn out designs that are ‘maybe’ DC correct but almost never good enough to actually attempt to use, in my experience.

I would always strongly, strongly encourage things to be hand routed. On simple boards it may not matter, but the only way you can tell whether it matters or not is by getting the boards back and testing them. Signal integrity failures are the worst to debug and will just be ‘the board works fine most of the time, then it doesn’t’. These are the failures that can soak a lot of time to find.

The other thing is that on simple boards, you might as well use those to develop the skills needed to do more complicated boards. I would have said that the pendant board already has enough routing on it to be quite complex to do well in a 2 layer board, just due to the number of traces.

This will also give you a feel for what the tradeoff is when adding extra stuff to soak up unused pins and how to do it effectively. Adding block headers like that is great for functionality, but it adds a lot of routing complexity. If I’m not sure I’ll use it, I’ll typically add them as single through-hole test points. That lets me wire something up manually if I need to use them and then I can add the proper hardware in a future revision if needed, without making the planned-for design significantly worse.

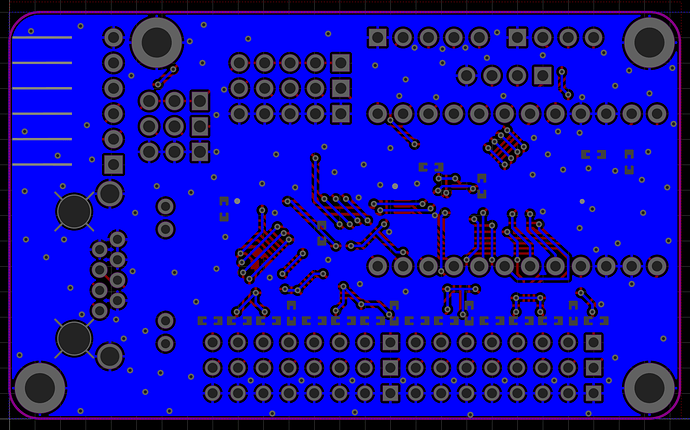

In terms of the issues with the above board, it comes back to the same stuff I was writing about in the 6-pack thread. For every single signal, you should be able to go through and draw a loop for where the current will flow. Even digital IO signals will have current flowing because input pins have capacitance, so every time a signal changes state, a small high-frequency burst of current will flow between the input and output pins on a net. That current will also have a closed loop path back to where it came from. The goal is to make that path as low inductance as possible, which we do by making the loop area as small as possible. Looking at some of those ground traces, the loop area is huge, which means that any current in the loop will radiate off the board and cause noise in the adjacent loops, as well as any noise externally (like a brushed router that’s basically a broadband noise generator, for instance) will be picked up by those loops like they’re an antenna.

My approach to routing a board like that would be to forget about the ground connections for the moment, try to route all the signal connections cleanly first, then get all the power connections routed, then go through and pour a ground polygon on the top and bottom layers to provide the power/signal return path. Try to keep connections to the top layer wherever possible. If you need to use the bottom layer, try to do it for brief hops then come back up to the top so you’re not cutting ‘slots’ in it. Try to group signals together so that you can get big unbroken chunks of ground plane. Then add vias everywhere that you can.

Other than that, is looks pretty good. I would also try to move all the designators on the silk layer so that they’re not touching any other silk and so that they’re not over the top of pads. I also try to keep them all the same orientation as the component (where it makes sense), as well as all in one of 2 orientations, so that they’re all either 0 degrees or 90 degrees for instance.